# DELTA

# "Development of SpaceWire and CAN SystemC Transaction Level Models for ESA IP cores"

SpaceWire TLM User Manual

# FINAL

# PUBLIC

Date: 25 November, 2010

Prepared by:

Qualtek Sprl. 36 Avenue Gabriel Emile Lebon, B-1160, Brussels, Belgium

For:

ESA-ESTEC Keplerlaan 1, Postbus 299, 2200 AG Noordwijk, The Netherlands

## Page intentionally blank

| TITLE                   | DELTA                 | "Development of SpaceWire and CAN SystemC Transaction Level Models for |               |  |

|-------------------------|-----------------------|------------------------------------------------------------------------|---------------|--|

| COPYRIGHT               | Copyright © 2010 Qua  | Copyright © 2010 Qualtek Sprl., Brussels, Belgium                      |               |  |

| CONFIDENTIA             | <b>ALITY</b>          |                                                                        | DISTRIBUTION  |  |

| Public                  |                       | X                                                                      | ESA-ESTEC     |  |

| Government Confidential |                       |                                                                        | Qualtek Sprl. |  |

| Military Config         | Military Confidential |                                                                        |               |  |

| REVISION HIS            | STORY                 |                                                                        |               |  |

| Version                 | Date                  | Author                                                                 | Status        |  |

| 1.0                     | 2 June, 2010          | Nikos Mouratidis                                                       | PRE-FINAL     |  |

| 1.1                     | 15 June, 2010         | Nikos Mouratidis                                                       | PRE-FINAL     |  |

| 1.2                     | 21 June, 2010         | Dimitris Tsaimos                                                       | PRE-FINAL     |  |

| 1.3                     | 30 June, 2010         | Nikos Mouratidis                                                       | PRE-FINAL     |  |

| 1.4                     | 28 September, 2010    | Dimitris Tsaimos                                                       | FINAL         |  |

| 1.5                     | 25 November, 2010     | Dimitris Tsaimos                                                       | FINAL         |  |

#### Public

## List of Changes

| Index | Change Description                                       | Revision | Date     |

|-------|----------------------------------------------------------|----------|----------|

| 1     | Minor editing/corrections                                | 1.1      | 15-06-10 |

| 2     | Addition of Section 5, minor additions to other sections | 1.2      | 21-06-10 |

| 3     | References to intermediate code version removed          | 1.3      | 30-06-10 |

| 4     | Description adapted to the changes in the implementation | 1.4      | 28-09-10 |

| 5     | Modifications suggested at the Final Review              | 1.5      | 25-11-10 |

|       |                                                          |          |          |

|       |                                                          |          |          |

|       |                                                          |          |          |

|       |                                                          |          |          |

|       |                                                          |          |          |

|       |                                                          |          |          |

|       |                                                          |          |          |

|       |                                                          |          |          |

|       |                                                          |          |          |

|       |                                                          |          |          |

## DOCUMENT APPROVED BY:

| PROJECT<br>MANAGER         | QUALITY<br>MANAGER | MANAGING<br>DIRECTOR | CUSTOMER'S<br>REPRESENTATIVE |

|----------------------------|--------------------|----------------------|------------------------------|

| Date:                      | Date:              | Date:                | Date:                        |

| Name:<br>Dr. N. Mouratidis | Name:              | Name:                | Name:                        |

| Signature:                 | Signature:         | Signature:           | Signature:                   |

|                            |                    |                      |                              |

## **Table Of Contents**

| Parag | Paragraph Pa                                                          |    |

|-------|-----------------------------------------------------------------------|----|

| 1 SC  | СОРЕ                                                                  | 8  |

| 1.1   | IDENTIFICATION                                                        | 8  |

| 1.2   | OVERVIEW                                                              | 8  |

| 1.3   | DEFINITIONS                                                           |    |

| 1.4   | DOCUMENT OVERVIEW                                                     | 9  |

| 2 AI  | PPLICABLE DOCUMENTS                                                   |    |

| 2.1   | ORDER OF PRECEDENCE                                                   |    |

| 3 DI  | EFINITIONS                                                            |    |

| 3.1   | TERMS AND DEFINITIONS                                                 |    |

| 3.2   | C++ CODE TERMS AND DEFINITIONS                                        |    |

| 4 CC  | ONFIGURATION MANAGEMENT                                               |    |

| 4.1   | DIRECTORY STRUCTURE                                                   |    |

| 4.2   | MODEL CONFIGURATION                                                   |    |

| 5 SF  | PACEWIRE CODEC TLM MODEL TIMING                                       |    |

| 5.1   | SPACEWIRE TLM TRANSACTION DELAYS                                      |    |

| 5.2   | IMPACT OF RTL MODEL CONFIGURATION OPTIONS ON DELAYS                   |    |

| 6 Fl  | JNCTIONAL OVERVIEW                                                    |    |

| 6.1   | System Overview                                                       |    |

| 6.2   | Functions                                                             |    |

| 6.3   | CONFIGURATION OVERVIEW                                                |    |

| 7 M   | ODEL ABSTRACTION LEVELS                                               |    |

|       | UILDING THE MODEL                                                     |    |

| 8.1   | NATIVE COMPILATION                                                    |    |

| 8.2   | MODELSIM COMPILATION                                                  |    |

| 8.3   | MODELSIM TEST-BENCH OUTPUT                                            |    |

| 9 M   | ODEL DEPLOYMENT                                                       | 25 |

| 9.1   | SPACEWIRE TLM MODEL CONFIGURATION                                     |    |

| 9.2   | SPACEWIRE TLM MODEL CONTROLLING AND SPACEWIRE TLM MODEL INSTANTIATION |    |

| 10    | TLM MODEL HOST-SIDE TRANSACTIONS                                      |    |

| 10.1  |                                                                       |    |

| 10.2  |                                                                       |    |

| 10.3  |                                                                       |    |

| 10.4  | STATUS REGISTER                                                       |    |

| 10.5  | CONTROL REGISTER                                                      |    |

| 10.6  |                                                                       |    |

| 10.7  |                                                                       |    |

| 10.8  | READING/WRITING TIMECODES FROM/TO THE SPACEWIRE CODEC TLM             |    |

| 11    | TLM MODEL NETWORK-SIDE TRANSACTIONS                                   |    |

| 11.1  |                                                                       |    |

| 11.2  | NETWORK-SIDE TRANSACTIONS CODING STYLES SUPPORT                       |    |

| 12    | CONCLUSIONS                                                           | 43 |

| APPEN | NDIX A DELTA SYSTEMC-ONLY TEST-BENCH DESCRIPTION                      |    |

| A.1.  | Test-Bench Arxchitecture                                              |    |

| A.2.  | DATA GENERATION AND VERIFICATION                                      |    |

| A.3.  | HOST SYSTEM CONFIGURATION                                             |    |

| A.4.  | PACKET ERROR INJECTION MECHANISM                                      |    |

| REFERE  | NCES                               | 50 |

|---------|------------------------------------|----|

| LIST OF | ACRONYMS                           | 49 |

| A.7.    | Delta Test-bench SystemC Processes | 48 |

|         | TEST-BENCH TERMINATION             |    |

| A.5.    | TEST-BENCH OPERATION               | 46 |

## List of Tables

| Table                                                                      | Page |

|----------------------------------------------------------------------------|------|

| Table 1: Overall code structure of SpaceWire TLM                           | 13   |

| Table 2: Overall structure of the RTL test-bench                           | 13   |

| Table 3: SpaceWire TLM Tx delay types                                      | 15   |

| Table 4: SpaceWire TLM Rx delay types                                      | 16   |

| Table 5: SpaceWire CODEC TLM configuration parameters (CDeltaSpacewConfig) | 28   |

| Table 6: CODEC TLM observation points compiler directives                  | 29   |

| Table 7: SpaceWire CODEC TLM-2.0 targets                                   | 33   |

| Table 8: CODEC TLM status register fields                                  | 35   |

| Table 9: CODEC TLM control register fields                                 | 36   |

| Table 10: Host emulator configuration class parameters                     | 45   |

| Table 11: Host emulator observation points                                 | 46   |

## List of Figures

| Figure                                                        | Page |

|---------------------------------------------------------------|------|

| Figure 1: SpaceWire CODEC TLM directory structure             | 12   |

| Figure 2: SpaceWire CODEC TLM block diagram                   | 17   |

| Figure 3: Delta transactor block diagram                      | 18   |

| Figure 4: Example of configuration class instantiation        | 31   |

| Figure 5: Example of model instantiation                      | 31   |

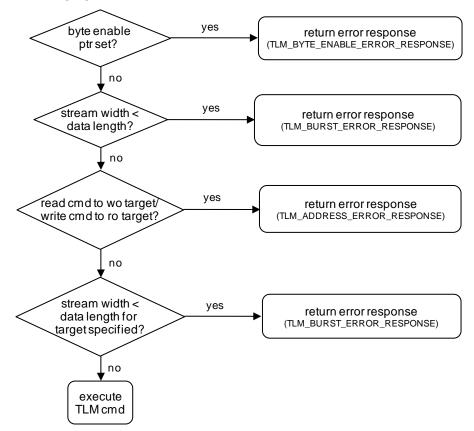

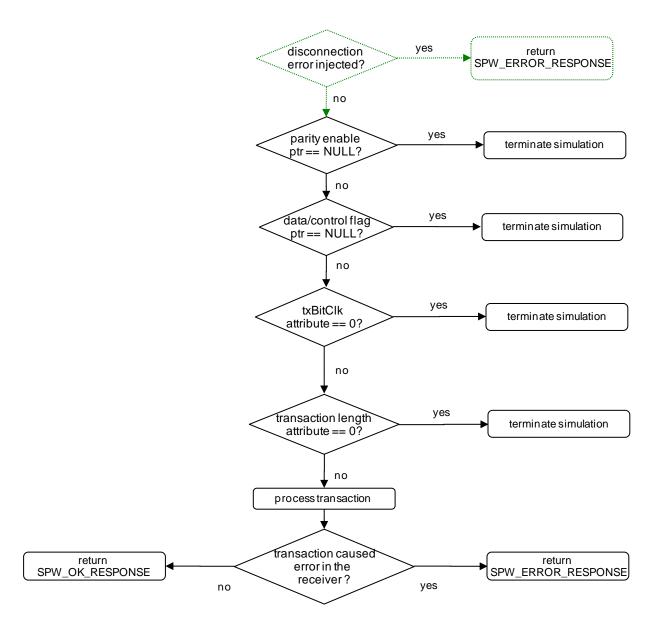

| Figure 6: CODEC TLM-2.0 transaction execution flow            | 32   |

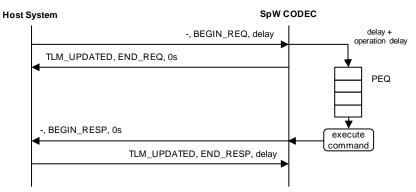

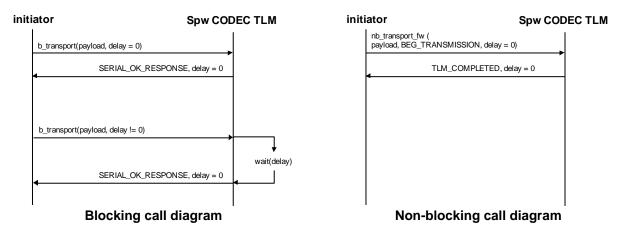

| Figure 7: CODEC TLM-2.0 AT transaction timing diagram         | 33   |

| Figure 8: Status register read example                        | 35   |

| Figure 9: Control register write example                      | 37   |

| Figure 10: Transmitter FIFO write example                     | 37   |

| Figure 11: Time code write example                            | 38   |

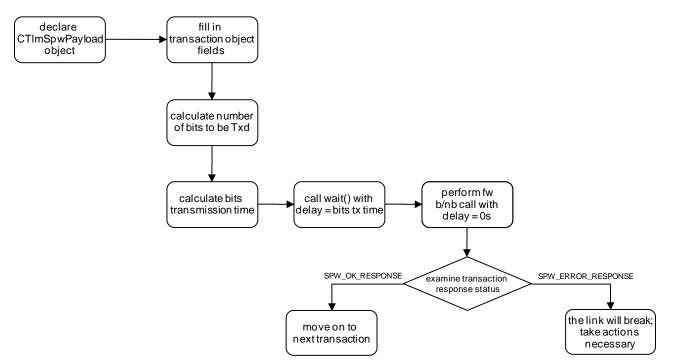

| Figure 12: SpaceWire network-side transaction execution       | 40   |

| Figure 13: SpaceWire network-side transactions timing diagram | 41   |

| Figure 14: SpaceWire transaction execution flow               | 42   |

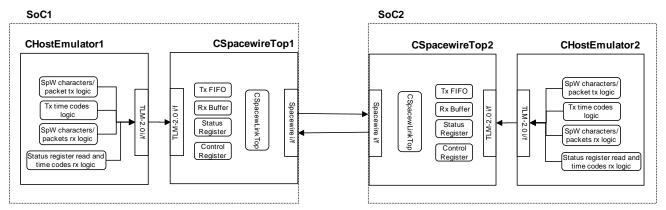

| Figure 15: SystemC-only testbench topology                    | 44   |

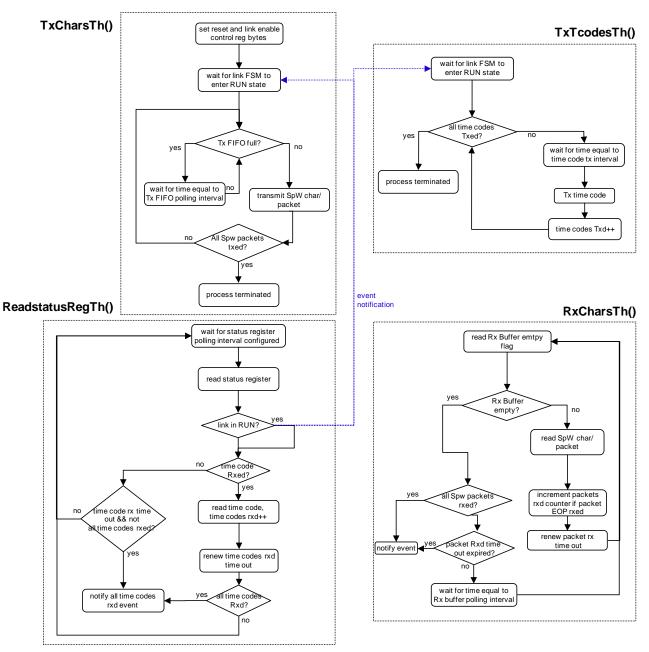

| Figure 16: CHostEmulator processes and relating logic         | 47   |

## 1 **SCOPE**

## 1.1 IDENTIFICATION

This document presents the usage of the SpaceWire TLM 2.0 core delivered by DELTA. It aims at providing the details necessary for a core user to utilise the model within a system-wide model.

## 1.2 OVERVIEW

The DELTA project has delivered a TLM 2.0 model of the SpaceWire IP that was already in existence in the form of a RTL core written in VHDL. The objective of the current project has been to provide leverage for the attainment of simulation models that execute faster and natively (i.e. without the need for a separate simulator application) on a host platform. The present document describes how the establishment of a system-wide model making use of the SpaceWire core is possible, using the developed core.

Although the core was, as stated before, targeting the instantiation of a standalone simulation environment, where the simulation kernel constitutes part of the model itself, it was agreed as part of the project related validation, that the TLM core would be assessed against the existing RTL IP. As such, the necessary infrastructure was put in place to allow the mixed simulation of a TLM (SystemC) core and a VHDL testbench. Since this infrastructure was created, utilisation of the developed TLM within it is also discussed in this document.

## 1.3 **DEFINITIONS**

## Shall

Identifies the mandatory requirements on the item or items. Statements which include the *shall* statement are to be considered as the only requirements to be tested or otherwise validated.

### Should

Suggests an approach that is to be assumed as the approach to be taken and is a reflection of the current status at the time of document issue. Terms such as '*may*' or '*can*' also fall into this advisory but not mandatory category.

## Will

Indicates factors that are imposed on the scope of this specification from outside and is to be regarded as a definition of factors that are mandatory by implication.

## 1.4 DOCUMENT OVERVIEW

This document is identified as follows:

| Document type       | - User Manual       |

|---------------------|---------------------|

| Document identifier | - 0310-01-004-01    |

| Revision            | - 1.5               |

| Issue Date          | - 25 November, 2010 |

## 2 APPLICABLE DOCUMENTS

The following documents of the exact issue shown form a part of this specification to the extent specified herein.

| RFQ/3-12785/09/NL/JK/al                   | The Request For Quotation provides details on the expected form of the delivered model in terms of use cases, as well as compatibility with or dependency on simulation tools.<br>Revision, November 10, 2009 |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSCI TLM-2.0 LANGUAGE<br>REFERENCE MANUAL | The LRM defines the classification, nomenclature, and details of the applicable coding style with reference to the model use cases. <b>Revision. JA32, July, 2009</b>                                         |

| SpaceWire CODEC IP -<br>User Manual       | The User Manual of the RTL IP core provides grounds for the utilisation<br>of the TLM together with the developed transactor in simulations,<br>replacing the RTL IP<br><b>Revision. 2.4, March 27, 2009</b>  |

## 2.1 ORDER OF PRECEDENCE

In the event of a conflict between the text of this specification and the references cited herein, **except references to higher-level program-unique specifications for this program**, the text of this specification takes precedence. Nothing in this specification however, supersedes applicable laws and regulations, unless a specific exemption has been obtained.

## 3 **DEFINITIONS**

## **3.1 TERMS AND DEFINITIONS**

| Bit rate | Number of bits transmitted/received every second                                                  |

|----------|---------------------------------------------------------------------------------------------------|

| byte     | Eight bits of information                                                                         |

| DDR      | Double data rate. Two bits of data transmitted for each transmit clock period.                    |

| FCT      | Flow control token. Transmitter sends one FCT when room in receive buffer for eight more N-chars. |

| N-char   | Data character, EOP or EEP.                                                                       |

| Null     | Control code transmitted by SpaceWire link to keep connection with other end.                     |

| SDR      | Single data rate. One bit of data transmitted for each transmit clock period.                     |

## 3.2 C++ CODE TERMS AND DEFINITIONS

The term ".h file" is used in this document to refer to the public interface file because of the longstanding Unix/C practice of using a ".h" extension to the file name, although other operating systems and compilers may require a different extension. The term ".cpp file" is used in this document to refer to an implementation file for similar historical reasons.

The interface file provides a single point of declaration of the data entities and functions provided by a particular module. The interface is #included in all modules which refer to or make use of the data entities and functions provided. Sections of the interface file are not copied into other modules.

The contents of the interface file are surrounded by #ifdef/#endif pre-processor directives in order to avoid problems of multiple inclusion.

## 4 CONFIGURATION MANAGEMENT

## 4.1 DIRECTORY STRUCTURE

The directory structure of the SpaceWire CODEC TLM is shown in the following diagram:

|              | root   |                |                    |

|--------------|--------|----------------|--------------------|

| RtlTestbench | ]      | SystemcSources |                    |

|              | GenTb  |                | CControlReg        |

|              | SpwrTb |                | CDeltaSpacewTract  |

|              | TbPkg  |                | CDeltaTestbench    |

|              | Тор    |                | CHostEmulator      |

|              | UutTb  |                | cmake_modules      |

|              | verif  |                | CRxDecode          |

|              | cmd    |                | CSpacewireTop      |

|              |        |                | CSpacewLinkTop     |

|              |        |                | CSpwInitiator      |

|              |        |                | CSpwTarget         |

|              |        |                | CStatusReg         |

|              |        |                | CTImTarget         |

|              |        |                | CTxEncode          |

|              |        |                | CUntimedFifo       |

|              |        |                | DeltaReporting     |

|              |        |                | DeltaScMain        |

|              |        |                | DeltaSpacewHeaders |

|              |        |                | ScEnumTrace        |

|              |        |                | SpacewSerial       |

## Figure 1: SpaceWire CODEC TLM directory structure

The SpaceWire CODEC sources, as well as the transactor sources are located under the SystemcSources directory, whereas the VHDL sources of the RTL test-bench along with the command files and scripts necessary to build the mixed SystemC-VHDL design and run the simulations are located under the RtITestbench directory.

A description of the SpaceWire CODEC SystemC sources directory is presented in Table 1:

| Directory         | Description of contents                                                |

|-------------------|------------------------------------------------------------------------|

| CControlReg       | SpaceWire CODEC SystemC model control register                         |

| CDeltaSpacewTract | The SpaceWire CODEC transactor class                                   |

| CDeltaTestbench   | The class implementing the SpaceWire CODEC SystemC-only test-<br>bench |

| CHostEmulator     | Traffic generator for the SystemC-only test-bench                      |

| CRxDecode         | Receiver and decoding logic                                            |

| Directory          | Description of contents                                                                                                                         |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| CSpacewireTop      | Top level module of SpaceWire CODEC TLM                                                                                                         |

| CSpacewLinkTop     | Top level module of SpaceWire CODEC network i/f, encapsulating the CODEC transmitter and receiver                                               |

| CSpwInitiator      | SpaceWire TLM protocol initiator class, implementing the SpaceWire initiator i/f towards the SpaceWire link                                     |

| CSpwTarget         | SpaceWire TLM protocol target class, implementing the SpaceWire target i/f to the SpaceWire link                                                |

| CStatusReg         | The SpaceWire CODEC status register                                                                                                             |

| CTImTarget         | TLM-2.0 Target class implementing the TLM-2.0 target i/f towards the host system                                                                |

| CTxEncode          | Transmitter and encoder logic                                                                                                                   |

| CUntimedFifo       | FIFO model for host interfacing option                                                                                                          |

| DeltaReporting     | Reporting functions for the creation of logs and monitors                                                                                       |

| DeltaScMain        | The SystemC-only test-bench entry point, implementing the sc_main method.                                                                       |

| DeltaSpacewHeaders | General purpose header files, including the definition of the CODEC configuration class and classes structures used in packet level simulations |

| ScEnumTrace        | Utility header file used to enable the waveform tracing of SystemC enumeration values                                                           |

| SpacewSerial       | The SpaceWire custom protocol and payload implementation                                                                                        |

### Table 1: Overall code structure of SpaceWire TLM

The description of the RtlTestbench sources directory is presented in Table 2:

| Directory | Description of contents                                                                                                                                                                                                                                 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GenTb     | RTL test-bench commands file parser and generic log messages printing component                                                                                                                                                                         |

| SpwrTb    | VHDL sources of the SpaceWire interface reference implementation,<br>sources of the components used to generate stimuli and traffic for the<br>reference implementation, verify data received by the reference<br>implementation and monitor its status |

| TbPkg     | VHDL packages for the test-bench                                                                                                                                                                                                                        |

| Тор       | RTL test-bench top-level component, instantiates the VHDL sub-<br>components along with the CODEC SystemC model                                                                                                                                         |

| UutTb     | VHDL sources of the components used to generate traffic and stimuli for the SpaceWire CODEC, verify data received by the CODEC and monitor its status                                                                                                   |

| verif     | scripts necessary to build the mixed VHDL-SystemC testbench and run the simulations                                                                                                                                                                     |

| cmd       | command files for the control and monitoring components of the RTL test-bench, used to form individual testing scenarios                                                                                                                                |

### Table 2: Overall structure of the RTL test-bench

## 4.2 MODEL CONFIGURATION

The SpaceWire TLM realises both the Loosely Timed and the Approximately Timed coding styles, as these are defined in the TLM 2.0 Language Reference Manual [1]. In addition, the model operates on two distinct levels of the SpW standard, namely at the exchange level, and at the packet level, as defined in [2]. The exchange level deals with transactions where the data quantity exchanged is the character, while in packet level, as the name suggests, a complete packet is transferred in every transaction, thus providing a higher level of data abstraction and leading to faster, albeit less detailed, simulations. Moreover, the user of the model is able to select any of the four possible combinations between coding styles and data abstraction.

The selection of the coding style, as well as the specification of all other model parameters takes place through the SpaceWire CODEC configuration class CDeltaSpacewConfig. The defined parameters are passed to all classes affected by the respective values. Therefore, a single point of reference and configuration exists for the entire model, and parameters are propagated throughout the model without the need for further user action. The Spacewire CODEC TLM model is complemented with a set of controllable observation points, realized as logging messages and VCD trace file waveforms. The observation points are enabled/disabled via compilation directives. Additional examples of configuration parameters include CODEC SystemC module names, initiator and target socket names, as well as custom address assignment to memory-mapped CODEC registers, such as the transmitter FIFO full flag and the receiver buffer empty flag. For a complete reference on the configuration options of the SpaceWire CODEC, the reader is referred to the SpaceWire CODEC Development Manual [6].

Finally, regarding the configuration registers of the SpaceWire CODEC, the corresponding RTL implementation does not actually implement them; it merely places the relevant input signals on the interface of the IP core, so that either the simulation test-bench or the surrounding logic can drive them. The same holds true for the status information generated by the core, for which output signals are used in the interface. The SpaceWire TLM model realises the corresponding functionality in the form models of registers, integrated to the host interface. In this manner, the model shall be controllable at run-time, a feature that is not directly supported by its RTL counterpart. Thus, since no implemented reference exists, it was decided that the mapping of control and status registers shall follow that of the SpaceWire core in the Gaisler Research GRLIB [5], and, in particular, that of GRSPW (as opposed to GRSPW2).

## 5 SPACEWIRE CODEC TLM MODEL TIMING

The development of the SpaceWire CODEC TLM model required the identification of the CODEC operations relating to transactions and the measurement of the corresponding delays, in order to achieve a timing accuracy level as close as possible to the one offered by the RTL CODEC model. Towards this end, the RTL CODEC model delays of interest were identified, measured from the RTL test-benches and assessed against the VHDL code of the RTL IP core.

## 5.1 SPACEWIRE TLM TRANSACTION DELAYS

Delays extracted from the RTL model are relating to both the transmitter and receiver blocks of the SpaceWire CODEC RTL model. Specifically, for the transmitter block the following timing measurements were performed

- start-up sequence delay of the SpaceWire CODEC transmitter,

- delay between a time code being written to the CODEC transmitter block and the transmitter identifying the time code request from the host system,

- SpaceWire characters transmission delay,

- transmission FIFO write delay,

- recovery controller timing.

The semantics of each delay type are summarized in the table below.

| Delay Type                                   | Description                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| transmitter start-up sequence delay          | Time interval between the transmitter being activated<br>and the first transition on the transmitter data and<br>strobe outputs.                                                                                                                                                                                                                                  |

| time code request delay                      | Time interval defined by the timing point the time<br>code controller writes a host time code to the<br>transmitter block and the timing point the transmitter<br>becomes aware of the time code request, thus<br>selecting the host time code as the next character to<br>transmit.                                                                              |

| characters transmission delay                | Time required for the transmitter to output all bits<br>corresponding to a SpaceWire character to the link,<br>i.e. the time between the first and last character bit<br>transmission.                                                                                                                                                                            |

| transmission FIFO write delay                | Time required for the host system to write a SpaceWire character to the transmission FIFO. depends on the timing of the actual FIFO deployed along with the model; for the purposes of the SpaceWire CODEC TLM model, the FIFO that comes together with the RTL model was used to extract the measurements.                                                       |

| transmitter block recovery controller timing | The CODEC recovery controller is responsible for<br>spilling the tail of the current packet when the link is<br>disconnected as the result of an error. In the RTL<br>model, the recovery controller operation is based on<br>a FSM, therefore the actual delay between<br>successive read operations performed by the<br>controller during the recovery process. |

#### Table 3: SpaceWire TLM Tx delay types

For the receiver block the timing measurements of interest are

- start-up sequence delay of the SpaceWire CODEC receiver,

- the time interval between a time code reception having been completed and the time code being available to the host system,

- the time interval between a data character reception having been completed and the data character storage to the receive buffer, from where it can be retrieved by the host system,

- the receive buffer error recovery delay.

The description of each delay type is included in the table below.

| Delay Type                           | Description                                                                                                                                                                                                                                                    |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| receiver start-up sequence delay     | Time interval between the first bit of the first character being received, and the first character reception being complete.                                                                                                                                   |

| time code reception delay            | The delay between the time code reception and the time code being available for the host system, dictated by the time code resynchronization delay.                                                                                                            |

| data character reception delay       | The delay between the data character reception and<br>the data character being available for the host<br>system, dictated by the data characters<br>resynchronization delay and the data characters<br>processing stages.                                      |

| receiver buffer error recovery delay | Time interval that elapses between an error in<br>SpaceWire characters reception being detected –<br>which causes the transition of the link FSM from the<br>RUN to the ERROR RESET state – and the receiver<br>block writing an EEP into the receiver buffer. |

#### Table 4: SpaceWire TLM Rx delay types

The resynchronization delays of the time code and data characters reception are introduced due to the use of different clock domains by the receiver block and the host system.

## 5.2 IMPACT OF RTL MODEL CONFIGURATION OPTIONS ON DELAYS

The RTL model contains a variety of configuration options for the SpaceWire CODEC. Amongst these, the ones that affect the transaction timing are the pipelining configuration option and the double data rate configuration option.

The pipelining option adds an extra transmitter bit clock period in the transmission of the first data character, and an additional receiver bit clock period in the reception of the first data character. The mechanism utilised in the RTL implementation introduces storage within long combinatorial paths, essentially shortening the critical path, and allowing the system to operate on a higher clock frequency. Thus, the mechanism introduces one additional clock cycle to the operation of the respective part of the system, which is compensated for by the higher overall speed the system is allowed to function at. As far as the TLM is concerned, the activation of the pipeline results in the addition of the extra clock cycle to the annotated delays. If the clock frequency is not increased, with respect to the system running with the pipeline disabled, the overall timing of the model shall indicate that the pipelined version runs slower than the non-pipelined one.

On the other hand, the double data rate configuration option, results in the transmitter block transmitting two bits every transmit bit clock period, effectively reducing the bit transmission time to half the time required when the transmitter is not using double data rate for the same transmitter bit clock.

## 6 FUNCTIONAL OVERVIEW

## 6.1 SYSTEM OVERVIEW

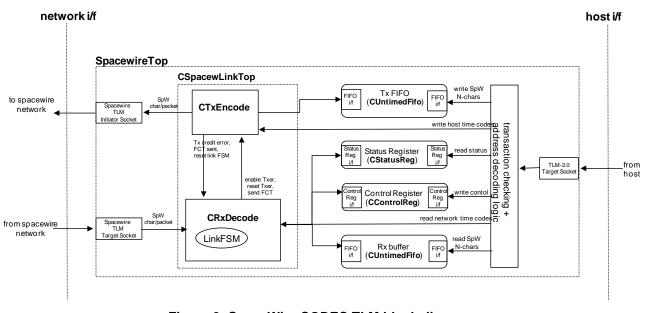

A block diagram of the SpaceWire CODEC and expected usage is given in the following figure.

Figure 2: SpaceWire CODEC TLM block diagram

## 6.2 FUNCTIONS

The transmitter block is implemented in the CTxEncode class. Its duties include reading data from the transmit FIFO and initiating transactions utilizing the TLM-2.0 interface. In order to adhere to the SpaceWire protocol flow control, the transmitter block maintains an internal credit counter indicating the number of data characters it can send across the link. In case the credit counter exceeds the maximum value defined by the SpaceWire standard – 56 characters – a credit error is identified and indicated to the link FSM. Additionally, it performs transmitter FIFO error recovery whenever the transmitter is disabled by the host or a request to flush the transmitter FIFO is issued.

The receiver block is implemented in the CRxDecode class. The receiver block processes incoming transactions, extracts SpaceWire characters and stores them into the receiver buffer. Time codes are identified and stored in a separate variable. The time code reception is indicated to the host system via setting a particular status register byte. Once the host reads the status register value it can acknowledge the new time code reception and read-in the time code received. The CRxDecode class also implements the flow control requirements of the SpaceWire protocol, by keeping a record of the number of entries the receive buffer can accept and requesting FCTs transmission from the transmitter block. Furthermore, the receiver block implements the SpaceWire link FSM, writes the status register bytes when necessary, and reads in the control register value whenever its contents are modified. Both the transmitter and receiver blocks are encapsulated in the CSpacewLinkTop class, whereas the complete TLM of the SpaceWire CODEC, including the transmitter FIFO, receiver buffer, status and control registers is enclosed in the CSpacewireTop class

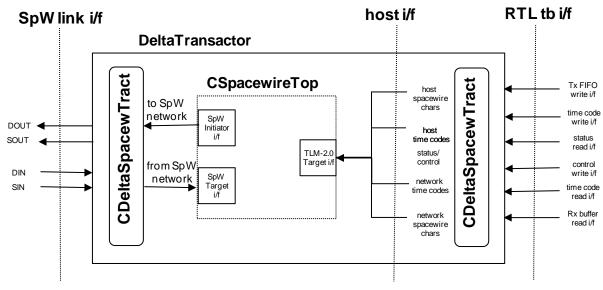

In order to enable the instantiation of the CODEC TLM model in the RTL test-bench of the RTL SpaceWire CODEC, a VHDL-to-SystemC and SystemC-to-VHDL translation component was realized, commonly reffered to as transactor.

The transactor functionality is implemented in the CDeltaSpacewTract class. It is responsible for translating VHDL signals to transactions for interfacing with the TLM model, and vice versa. The existence of the transactor allows the utilisation of both the RTL test-bench developed for the IP core, and provides the capability to the user to arbitrarily utilise the SystemC model within a HDL simulation, provided the deployed simulator is compliant to this mode of operation. The CSpacewireTop class, which embodies the complete TLM of the SpaceWire CODEC, along with the

#### Public

transactor functionality are encapsulated in the DeltaTransactor class, which constitutes the top level module instantiated in the VHDL test-bench. As such, the model shall be usable in exactly the same fashion as its RTL counterpart; in the latter case, the SpaceWire CODEC IP User Manual [3] shall be applicable to a great extent to guide the utilisation of the model/transactor composite. A block diagram of the DeltaTransactor component is provided in the figure below.

Figure 3: Delta transactor block diagram

## 6.3 CONFIGURATION OVERVIEW

In accordance to its RTL counterpart, the SpaceWire TLM can be configured to suit the applications of the users as follows:

- Pipelined or non-pipelined.

- DDR outputs or SDR outputs depending the on required data rate and the users selected technology.

- Transmission clock configuration options to allow an independent transmit clock and default reference clock therefore greatly increasing the achievable data rate and decoupling the transmit logic from the system clock logic.

- Capability to discard empty packets i.e. EOP followed by EOP/EEP and EEP followed by EOP/EEP.

- Ability to reserve host time codes for transmission even when the link is not running.

- Configurable receive buffer/transmit FIFO size.

Furthermore, a number of user-configurable parameters specific to the TLM implementation have been introduced. These include the names and IDs of model components, storage width and depth, etc.

## 7 MODEL ABSTRACTION LEVELS

The SpaceWire CODEC model operates at two abstraction levels, the packet and the exchange level. The abstraction levels are differentiated by the data transfer unit utilized in network-side transactions. As its name suggests, at the packet level model entire SpaceWire packets are carried in each transaction between the SpaceWire link ends. Specifically, in the packet level mode of operation while the interface to the host system remains the same as in the exchange level, meanly each Tx FIFO/Rx buffer write/read transaction carries a single Spacewire character, a transaction on the network side is only performed when an entire packet is available in the Tx FIFO. To realize this approach, the Tx FIFO not empty flag is only asserted when the host system has stored an entire packet for transmission.

At the exchange level, single SpaceWire characters are carried in both host-side and network-side transactions. The SpaceWire characters are stored to the transmitter FIFO, mapped by the transmitter block logic to the custom SpaceWire payload fields and transferred to the other end of the link via TLM transactions. The other end of the link is expected to extract the SpaceWire character from the transaction and store it to the receiver buffer if necessary. An in-depth description of the custom SpaceWire payload, as well as of the data structures used at the packet level model can be found in [6], whereas example code for writing/reading SpaceWire packets or characters to/from the transmitter FIFO/receiver buffer, can be found in the class emulating the host system – CHostEmulator.cpp – instantiated in the example SystemC-only test-bench that comes along with the model.

## 8 BUILDING THE MODEL

## 8.1 NATIVE COMPILATION

The SpaceWire TLM is developed with the purpose of being deployed in system-level simulation models, fully comprised of SystemC TLM building blocks. As such, it is a SystemC implementation, relying on the existence of the SystemC simulation kernel and the TLM library, in order to be compiled with the use of a C++ compiler. In order to make the compilation of the model files easier, the build structure is based on the CMake system, and the GNU gcc compiler. The SpaceWire TLM has been developed using the OSCI SystemC-2.2.0 library, the OSCI TLM-2.0.1 library, and the Greensocket-4.1.0 library, whereas it has been successfully compiled using gcc-4.4.3.

The organisation of the model encompasses a set of *CMakeLists.txt* files which describe the structure of the code and its distribution in files and folders. During the build process, the CMakeLists.txt file included in every sub-folder instructs the creation of a static library from the \*.cpp files located in the *src* sub-folder. If the creation of the static library requires header files from other sub-folders, cmake *find\_package* directives are used to locate the header files necessary.

The SystemC, TLM and Greensockets packages required for the TLM model to be built, are searched for in the top level CmakeLists.txt so that they become available for all sub-modules. The SystemC package contains both header files and the SystemC static library while the other two packages contain only header files. Two alternatives are provided for locating the packages necessary. The first solution demands the user to manually define the SystemC, TLM, and Greensocs libraries installation directories during the cmake command-line invocation as follows:

- -DSYSTEMC\_INSTALL:string={path to systemc static lib folder, include folder is assumed to be reachable by appending ../include},

- -DTLM\_INSTALL:string={path to TLM installation, include folder is reached by appending include/tlm},

- -DGREENSOCKS\_INSTALL:string={path to Greensockets installation, include folder is reached by appending greensocket}.

The second option assumes that *updatedb* has been executed after the installation of the above packages. The *updatedb* command may be executed with a local scope (i.e. updatedb ---localpaths='<path to files of interest>'), only to insert to the filesystem database the files of interest. For each package XXX, a FindXXX.cmake script exists in the cmake-modules subfolder of the source code tree. The FindXXX.cmake script uses *locate* to find potential folders containing the appropriate header files and/or static libraries. In both cases the header/library files in the candidate folders are checked against the versions used during model development; if the verification succeeds, the header/library location is assigned to the XXX\_INCLUDE\_DIRS and/or XXX\_LIBRARIES variables, where XXX is the library name. The SystemC library is considered valid if version "TLM 2.0.1 --- 2009-07-15" is reported. The libraries verification procedure requires compilation and execution of testing code included in the FindXXX.cmake scripts. The *dirline.sh* script in the root folder is used by the FindXXX.cmake scripts.

In order for the code to be fully compiled, the user needs to generate a build folder at the top-level of the file hierarchy. Using a command console, and once in the aforementioned "build" folder, the user issues the command:

cmake ../

or the command

cmake -DSYSTEMC\_INSTALL:string={pathto} -DGREENSOCKS\_INSTALL:string={pathto}

-DTLM\_INSTALL:string={pathto} ../

depending on the method used to locate the SystemC, TLM and Greensockets libraries. The cmake invocation generates the appropriate makefiles, therefore once its execution is completed, the command

make

should be issued, in order to build the complete model. As mentioned earlier, during the model build process, in the root folder of the project a sub-folder named *cmake\_modules* is created. This folder is appended to the default cmake path that is used for locating FindXXX.cmake modules that aid the discovery of packages containing header files and/or static libraries necessary for building the CODEC TLM model. The final executable *DeltaTestbench* is created inside the DeltaScMain sub-folder of the Build directory.

Users of the model may study the source code of the testbench (CDeltaTestbench.cpp) to gain insight on the instantiation of the model within a virtual platform; they may also use the test-bench as a template for the creation of such a platform, by adding instantiation of other models or components.

## 8.2 MODELSIM COMPILATION

The TLM model produced in DELTA is distributed in two basic folder structures: the former contains the model files, together with the files utilised by the CMake system; the latter contains VHDL testbenches and associated command files, as well as Modelsim command files, used for the compilation of the SystemC and VHDL file, and the loading of the simulation model. The following text describes the process necessary to compile and instantiate the model within Modelsim.

The provided DeltaRunVerif.tcl file, located in the RtITestbench/verif sub-folder, is the script that contains the commands required to build the mixed SystemC-VHDL simulation and load the simulation scenario the model user wishes to be executed. The DeltaRunVerif.tcl file is in essence a modification of the run\_verif.tcl script used to simulate the RTL CODEC model, including commands and invocation of scripts to compile the CODEC TLM model. As such, its invocation is identical to the run\_verif.tcl script of the RTL model. Specifically, the script file is run from the Modelsim shell by issuing the following command when in the RtITestbench/verif sub-folder

#### #do DeltaRunVerif.tcl <args>

Script arguments <args> are

| 1 0 0                                   |                                                                                                                                                                                                  |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -help                                   | Prints a help message on how to run the script.                                                                                                                                                  |

| -logwlf                                 | Log all signals to wlf files using "add log -r /*" before run -all.                                                                                                                              |

| -config <id></id>                       | Run configuration $\langle id \rangle$ where $\langle id \rangle$ can be 1, 2, etc. or can be all to run the full suite of test configurations. Valid configuration IDs are in the range 1 – 83. |

| -config_range <low> <high></high></low> | Run a range of configurations from low to high inclusive. There are a total of 83 configurations.                                                                                                |

In order for a simulation run to be performed, a specific model configuration or a configuration range must be specified with the -config <id> or the -config\_range <low> <high> arguments.

The DeltaRunVerif.tcl script invokes the DeltaModelComp.tcl file to compile the SpaceWire CODEC TLM sources. In order for the SystemC sources to be compiled, the following paths must be set-up inside the DeltaModelComp.tcl script, prior to running the DeltaRunVerif.tcl.

- 1. SPACEW\_SRC\_DIR points to the root of the SystemC sources,

- 2. SYSTEMC\_SRC\_DIR points to the Modelsim SystemC libraries, required by the Modelsim SystemC compiler, sccom,

- 3. TLM\_SRC\_DIR points to the OSCI TLM library sources,

- 4. GREEN\_SOCKET\_DIR points to the root of the Greensocket library sources.

The DeltaModelComp.tcl script also creates a header file – DeltaMsim.h – inside the SPACEW\_SRC\_DIR/DeltaSpacewHeaders/include sub-folder. The particular header file contains the definitions of SpaceWire CODEC TLM and transactor parameters which are necessary for compiling the SystemC sources and can not be assigned at run time - specifically the CODEC transmission FIFO and receiver buffer depths - as well as the width in bits of configurable transactor input ports.

### Public

It should be noted that only the AT, exchange level model of the SpaceWire CODEC can be deployed in the Modelsim simulation, as the packet level model is too abstract for the RTL testbench, whereas the LT, exchange level model does not provide the timing accuracy necessary to execute the RTL model test suite. Additionally, the definition of the kind of log messages the user wishes the TLM model to print, should be defined in the DeltaModelComp.tcl script by setting the relating compilation directives to be used when Modelsim invokes the C++ compiler. The CODEC configuration class instantiation in the CODEC top-level component is defined in the SPACEW\_SRC\_DIR/CDeltaSpacewTract/include/CDeltaSpacewTract.h file, which also contains the instatiation of the top-level SystemC module used in the mixed language simulation, which encapsulates the transactor and the Spacewire CODEC TLM model. One point to note here, is that there are a number of CODEC parameters in the Modelsim simulation which are set-up during the simulation run time and therefore the setting of the particular parameters by the model user has no effect. The following list summarizes the CODEC TLM configuration class parameters which are assigned during simulation run time. For each parameter, the corresponding CODEC configuration class member variable is enclosed in parentheses:

- pipelining configuration (cfgPipeline),

- DDR configuration (cfgDdrOut),

- whether the receiver buffer read clock will be synchronous to the system clock or not (cfgSyncRdClk),

- the system clock period duration (sysClkPeriod),

- the transmit bit clock period duration (txBitClkPeriod),

- the receive buffer read clock period duration (rdClkPeriod),

- whether time codes will be discarded when the link is not in the RUN state (cfgTickInKeep),

- whether empty packets will be discarded (cfgDiscardEmptyPkt),

- The transmission bit clock configuration (txClkCfg).

This is due to the fact that these parameters are specific to each test configuration and are decided during the selection of the configuration to be run. In the RTL model simulation, the aforementioned parameters are either defined via test-bench command files, or in the configuration-specific working\_spwrlink\_pkg.vhd file, created by the run\_verif.tcl script. In the TLM model, they are realized as parameter values, assigned to the relating configuration class members during the transactor class construction. In particular, the DeltaRunVerif.tcl script writes the values of the aforementioned parameters into a text file – SystemcSpwCodecConfig.txt – and the transactor constructor reads in and assigns the values to the configuration class members.

The SpaceWire TLM model has been tested with Modelsim SE version 6.5d. It should be noted that Modelsim comes with a gcc compiler, which is the one utterly used by sccom; the gcc version included in Modelsim 6.5d is 4.1.2. In case the model user wishes to use another compiler, he/she may do so by specifying the path to the compiler executable via the -cpppath option of the Modelsim sccom compiler. The sccom command is invoked in the DeltaModelComp.tcl script.

## 8.3 MODELSIM TEST-BENCH OUTPUT

During the test runs, the test-bench generates console logs informing the model user about the simulation progress. The console log messages originate either from the RTL test-bench components, or from the SpaceWire TLM model components. RTL test-bench logs are preceded by the current simulation time and contain the command status, as well as the actual RTL test-bench component command in capitalized letters. For example, the log message

# 593500 ns: > Command Complete: UUT\_DATA\_CTRL TRANSMIT\_PACKET T150us AAAA 100 01

informs the model user that the UUT\_DATA\_CTRL RTL test bench component has completed the transmission of a SpaceWire packet, and, in particular, it has stored the last SpaceWire character of

the packet into the transmit FIFO. For a complete reference of the RTL testbench components commands, refer to [4].

On the other hand, SpaceWire TLM logs fall under three categories

- 1. Informational messages,

- 2. Warning messages,

- 3. Fatal messages.

All three message types result in log messages being output to the console, whereas fatal messages also result in the current simulation run being terminated. Each log message consists of two lines and has the following format: the first line contains the type of the message, the name of the source file which contains the process that issued the message, the simulation time at which the log message was issued and the name of the process issuing the message. For instance:

Info:/home/dimitris/Projects/Delta/spacewire/SystemcSources/Debug/CRxDecode/src/CRxDecode.c pp: 176700 ns - ExecuteLinkFsmM

## CODEC\_1\_RxDecode : 140 - LINK FSM IN RUN STATE

where Info is the message type, the path following the semicolon is the path to the source file, 176700ns is the simulation time at which the message was issued and ExecuteLinkFsmM is the name of the process issuing the log message. The second line contains the actual log message, preceded by the SpaceWire CODEC module ID. In the particular case, the log message originates from the SpaceWire CODEC link FSM - which is implemented inside the receiver block source file CRxDecode.cpp – and informs the user that the link FSM is in the RUN state.

The exact message types generated depend on the observation points enabled by the model user. If for example the model user has activated the host target i/f transactions logging in the CODEC top-level module and the AT model was simulated, a TLM-2.0 transaction log messages sequence would be the following – the path to the source file has been deliberately trimmed for a better understanding of the log messages:

Info: /CTImTargetTop.cpp: 115490 ns - nb\_transport\_fw

CODEC\_1 : 100 TRANSACTION MOVED TO SEND-RESPONSE PEQ. RETURNING UPDATED (GP, END\_REQ, 0 s) TO FORWARD NB CALL.

Info: /CTImTargetTop.cpp: 115530 ns - BeginResponseM

CODEC\_1 : 100 STARTING BEGIN RESPONSE METHOD. PERFORMING READ OPERATION.

Info: /CTImTargetTop.cpp: 115530 ns - BeginResponseM

CODEC\_1 : 100 CALLING nb\_transport\_bw(GP, BEGIN\_RESP, 0 s).

Info: /CTImTargetTop.cpp: 115530 ns - BeginResponseM

CODEC\_1 : 100 nb\_transport\_bw RETURNED COMPLETED (GP, END\_RESP, 0 s)

The log message sequence above informs the model user that the SpaceWire top-level module received a non-blocking forward call at 115290 ns, and placed the relating transaction object into the payload event queue of the begin response method. Forty nanoseconds later at time 115530ns, i.e. after one receiver buffer clock cycle has elapsed, the transaction is retrieved from the PEQ and the Begin Response method is executed. The method performs the command included in the transaction payload – a TLM\_READ command in the particular case – and calls the backward non-blocking method with a phase equal to BEGIN\_RESP and a delay annotation equal to 0ns. Thereafter, the transaction is completed, since the non-blocking call returned an updated phase equal to END\_RESP.

Upon successful completion of a test scenario, the mixed-language test-bench prints the following message:

## # \*\* Failure: Testbench finished (all commands completed)

The AT, exchange level model CODEC TLM has successfully passed the entire suite of the RTL tests - all test scenarios from 1-83, whereas the LT, exchange level model fails on the execution of the tests, as it does not incorporate the timing accuracy necessary. Specifically, the LT model fails the majority of the RTL tests due to the timing inaccuracy introduced by the substitution of the SystemC process used to set the time code transmission request flag with a plain function call. This has the side effect of not scheduling the setting of the flag indicating the host request for the transmission of a time code after the delay interval extracted from the RTL model, but setting the relating flag immediately. During simulation, the CODEC TLM is first instructed to transmit a time code, and then the Spacewire link FSM is immediately disabled, in order for the time code to not be transmitted. In the AT model, the delay between the time code transmission request and the assertion of the time code transmission request flag, ensures that the link is disabled prior to the assertion of the request flag and therefore the time code is not transmitted. In the LT model however this delay is not accounted for, therefore the time code transmission request flag is asserted prior to the link being disabled. Due to the fact that the configuration parameter that permits a time code request to be reserved even if the link is not in the RUN state is set, the time code request flag remains asserted until the link enters the RUN state again, and the time code is transmitted though it should not. The test-bench then fails issuing the following message:

## # Testbench failed in TB\_SPWR\_STATUS TICKOUT VAL\_ALWAYS\_EQUALS T50us T1ns 0

In addition, the RTL test-bench tests scenarios require mechanisms provided by the exchange level model to be performed, such as flow control and parity checking. Hence, they are not applicable to the packet-level model implementation of the TLM. For example, the RTL test-bench examines the detection of various errors by the unit under test, transmitting SpaceWire character sequences causing such errors. For instance, a receiver credit error is induced to the unit under test via transmitting more characters than the unit under test has requested, a transmitter credit error is induced via the transmission of a series of FCTs in order to cause the transmitter of the unit under test to exceed its maximum credit, or an escape sequence error is generated by transmitting successive ESC characters. As the packet-level model, in addition to adhering to more relaxed timekeeping as compared to the exchange-level, cannot by definition support such mechanisms, it cannot be subjected to the RTL test-bench verification process either.

## 9 MODEL DEPLOYMENT

The present chapter provides details on the deployment of the SpaceWire TLM, targeting a SystemC simulation model. Details on the configuration of the model are provided, and its interface towards other components for the development of a system-wide model is discussed.

## 9.1 SPACEWIRE TLM MODEL CONFIGURATION

The SpaceWire TLM model components can be configured via the CODEC configuration class, which defines a number of public member variables; each variable holds a model configuration option. The configuration class, namely *CDeltaSpacewConfig* (CDeltaSpacewConfig.cpp), provides a centralized configuration point for the entire model, where component-specific parameters are defined, along with parameters that dictate the system-wide behaviour, extracted from the RTL model. The SpaceWire CODEC TLM accepts a pointer to the configuration structure as a constructor argument, thus granting access to the configuration options for the components it encapsulates. In general, the configuration options fall under the following categories

- simulation type,

- time codes transmission options,

- RTL model extracted options,

- clock period configuration,

- address configuration,

- naming and identification assignment,

- CODEC buffering.

Simulation type options are relating to the CODEC abstraction level used in a simulation, i.e. packet or exchange, as well as the coding style to be used, LT or AT. Additionally, for packet level simulations, the model can be configured to ignore errors injected in packets. Time codes transmission options enable the CODEC to transmit time codes, whereas they also provide a backdoor to circumvent the Spacewire standard requirement that a single node must transmit time codes in a Spacewire network. However, the particular option allowing a Spacewire CODEC to both transmit and receive time codes is provided for functional test purposes only, and should not be set in a realistic simulation scenario.

Options extracted from the RTL model define behavioural and timing aspects of the TLM. Specifically, the model can be instructed to take into account the timing implications induced by the use of pipeline and/or double data rate outputs. Additionally, thresholds can be set for the model programmable empty flag - i.e. the number of SpaceWire N-char entries the receiver buffer should contain for the flag to be unset; this feature could be used for the incorporation of a DMA controller in the SoC, which would handle the transfer of N-chars/packets from the receiver buffer to host system memory. Thresholds can be also set for the maximum number of outstanding N-chars the CODEC receiver should expect, and consequently the number of FCTs that should be transmitted by the CODEC. Under normal operating conditions this should be set to the receiver buffer depth. however smaller values are permitted. It should be noted though that if the value configured exceeds the buffer storage capability, it is ignored and the buffer depth is used as the outstanding N-chars limit. Furthermore the maximum transmitter credit allowed - the number of SpaceWire Nchars the transmitter can send – can be set. The transmitter credit is incremented every time a FCT is received, and if the credit available exceeds the value configured, a transmitter credit error occurs. In order to be compliant with the SpaceWire protocol, the maximum transmitter credit should be set to 56. Finally, the CODEC TLM can be instructed to reserve time codes received from the host system when the link is not running until the link enters the RUN state, whereas the empty packets handling behaviour, i.e. whether empty packets are discarded or not, can be set as well. One point to note here regarding time codes handling, is that the RTL CODEC does not utilize a buffer to store all time code requests from the host. Therefore, in spite of the system being configured to reserve time codes, a time code shall be overwritten by the next one. Therefore only the most recently received time code will be transmitted once the link enters the RUN state.

The RTL CODEC model includes a plethora of clock configuration options, the majority of which are concerned with the way the clocks are physically generated. Since the clocking options have a direct impact on the deployment of resynchronization flip-flops which are added to the SpaceWire characters/time codes data path and in certain cases affect the data path timing, they are incorporated as a configuration parameter. Additionally, for the purposes of the TLM the clock period durations also affect the timing of data-related operations. Hence, the SystemC CODEC model system clock, transmission clock and receiver buffer read clock periods can be defined. The system clock period is used in calculating the delay relating to transmission FIFO operations – reading the fifo full flag, writing SpaceWire N-chars to the FIFO, reading from and writing to the status and control register respectively, writing the host time code to the transmitter block and reading the time code received from the receiver block. The transmission clock affects the characters transmission timing, as it defines the bit clock period and therefore the time interval required for a character transmission to be complete. Finally, the read receiver buffer clock affects the delay of the receiver buffer empty flag and SpaceWire N-chars read operations.

The CODEC address configuration options define the addresses of the CODEC model memorymapped locations, in particular the transmission FIFO and receiver buffer along with the relating full/empty flags addresses, as well as the transmitter block host time code register and receiver block network time code addresses. Most of the aforementioned locations do not correspond to RTL model registers, with the obvious example being the FIFO/buffer full/empty flags, but have been modelled as such in the TLM. Last but not least, the memory map of the CODEC status and control register was based on the GRSPW SpaceWire core of the GRLIB, thus these addresses are hardcoded in the codec configuration class as static const variables.

The naming and identification assignment options enable the model user to assign meaningful IDs and names to the model building blocks, in order to gain observability of the events logged (e.g. to identify easily which components produced what events in the log). CODEC buffering options allow for the selection of the transmitter FIFO and receiver buffer depths and widths. However, the width values should not be set arbitrarily; the selection of the actual buffer width values depends on the simulation level used – packet or exchange. The overall configuration parameters are summarized in the following table, in the order they are declared in the CODEC configuration class.

| Parameter            | Туре                      | Description                                                                                                                                                                                                   |

|----------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | Simulation Type           | e Options                                                                                                                                                                                                     |

| tlmCodingStyle       | enum<br>TTImCodingStyle   | TLM coding style to be used – LT or AT                                                                                                                                                                        |

| spwAbstractLevel     | enum<br>TSpwAbstractLevel | Simulation abstraction level – packet or exchange                                                                                                                                                             |

| ignoreErrorInjection | bool                      | Ignore errors injected into SpW packets – valid only for packet level simulations                                                                                                                             |

| tcodesSendEnable     | bool                      | Enables the CODEC TLM to send time-codes. If set to false, the CODEC will not transmit time codes received from the host system.                                                                              |

| multipleTcodeMasters | bool                      | Enables the CODEC TLM to both send and<br>receive time-codes when set to true, thus<br>bypassing the Spacewire standard requirement<br>that a single node in a Spacewire network must<br>transmit time codes. |

|                      | RTL model-Extrac          | ted Options                                                                                                                                                                                                   |

| spacewMaxCredit      | unsigned char             | Maximum transmitter credit allowed – should be set to 56 for SpW protocol compliance                                                                                                                          |

| cfgRxBufProgVal      | unsigned char             | Receiver buffer programmable empty flag<br>threshold. The flag is set to true if the number of<br>buffer entries <= threshold                                                                                 |

| cfgDdrOut            | bool                      | use DDR outputs                                                                                                                                                                                               |

| Parameter                  | Туре                 | Description                                                                                |

|----------------------------|----------------------|--------------------------------------------------------------------------------------------|

| cfgPipeline                | bool                 | Use pipeline in the transmitter and receiver blocks                                        |

| cfgTickInKeep              | bool                 | Keep host time codes when the link is not in the RUN state                                 |

| cfgDiscardEmptyPkt         | bool                 | Discard empty packets – EOP followed by EOP/EEP, EEP followed by EOP/EEP                   |

| cfgMaxCredit               | unsigned char        | Maximum N-chars expected – should be set equal to the receiver buffer depth                |

| txClkCfg                   | enum<br>TTxClockCfg  | Transmission bit clock configuration options, as defined in [3]                            |

| cfgSyncRdClk               | const bool           | Indicates whether the receiver buffer read clock is synchronous to the system clock or not |

|                            | Clock Period Confi   | guration Options                                                                           |

| systemClkPeriod            | sc_time              | System clock period                                                                        |

| txerBitClkPeriod           | sc_time              | Transmission bit clock period                                                              |

| rdClkPeriod                | sc_time              | Receiver buffer read clock period                                                          |

|                            | Address Configu      | Iration Options                                                                            |

| netTcodeAddr               | unsigned int         | Time code received register address                                                        |

| hostTcodeAddr              | unsigned int         | Time code to transmit register address                                                     |

| rxBufferAddr               | unsigned int         | Receiver buffer address                                                                    |

| rxBufEmptyFlagAddr         | unsigned int         | Receiver buffer empty flag address                                                         |

| rxBufProgFlagAddr          | unsigned int         | Receiver buffer programmable flag address                                                  |

| txFifoAddr                 | unsigned int         | Transmission FIFO address                                                                  |

| txFifoFullFlagAddr         | unsigned int         | Transmission FIFO full flag address                                                        |

| Component                  | specific Naming, Ide | ntification, Debugging Options                                                             |

|                            | Status Regis         | ter Options                                                                                |

| statusRegId                | unsigned int         | Status register ID                                                                         |

|                            | Control Regis        | ster Options                                                                               |

| controlRegId               | unsigned int         | Control register ID                                                                        |

|                            | SpaceWire T          | op Options                                                                                 |

| spacewTopId                | unsigned int         | SpaceWire top module ID                                                                    |

| spacewTopModuleName        | char*                | SpaceWire top module name                                                                  |

| spwTopTImTargetSockName    | char*                | SpaceWire top TLM-2.0 target socket name                                                   |

| spwTopSerialTargetSockName | char*                | SpaceWire top SpaceWire target socket name                                                 |

| spwTopSerialInitSockName   | char*                | SpaceWire top SpaceWire initiator socket name                                              |

| spacewLinkTopModuleName    | char*                | SpaceWire link top module name                                                             |

|                            | Transmitte           | r Options                                                                                  |

| txld                       | unsigned int         | Transmitter block ID                                                                       |

| txEncodeName               | char*                | Transmitter block name                                                                     |

|                            | Receiver             | Options                                                                                    |

| rxld                       | unsigned int         | Receiver block ID                                                                          |

| rxDecodeName               | char*                | Receiver block module name                                                                 |

| Parameter                | Туре              | Description                                                                                                                     |  |

|--------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------|--|

|                          | Receiver Buffer ( | Options                                                                                                                         |  |

| rxBufDepth               | unsigned int      | Receiver buffer depth in entries                                                                                                |  |

| rxBufWidth               | unsigned int      | Receiver buffer width in bytes – should be set to 2 for exchange level and to sizeof(void*) for packet level                    |  |

| Transmitter FIFO Options |                   |                                                                                                                                 |  |